My Circuit Analysis

YouTube video: PC9XC Variable Gate Circuit

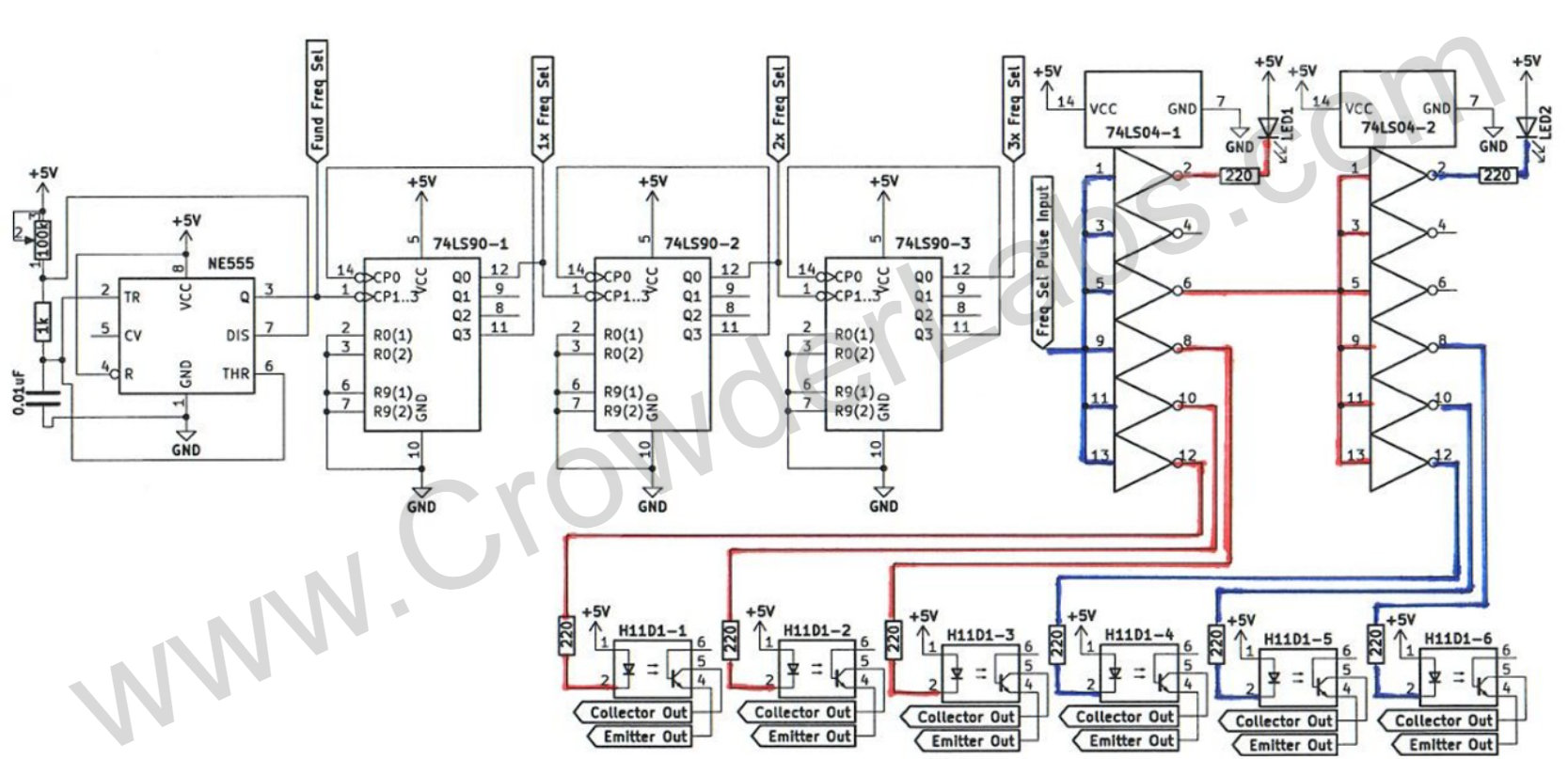

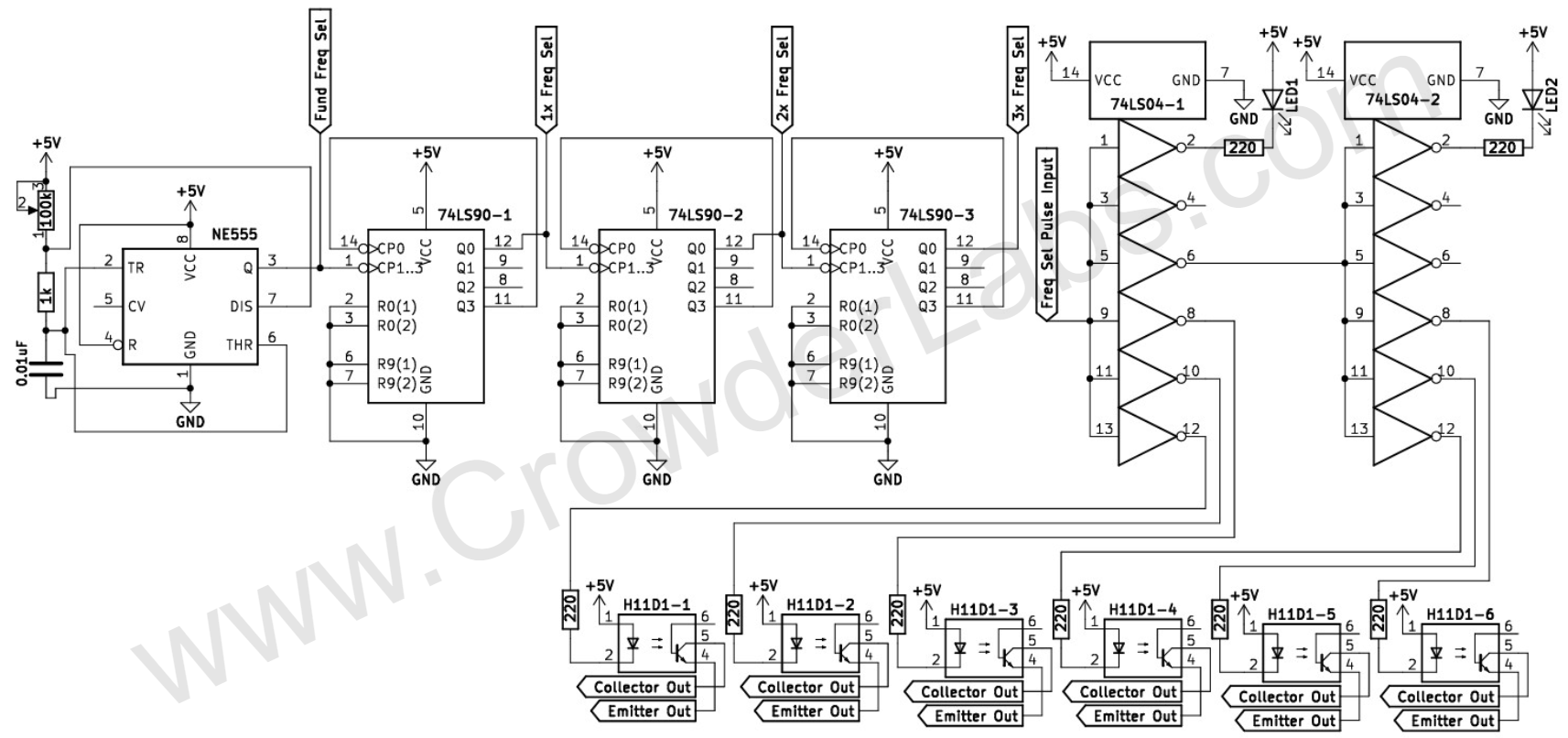

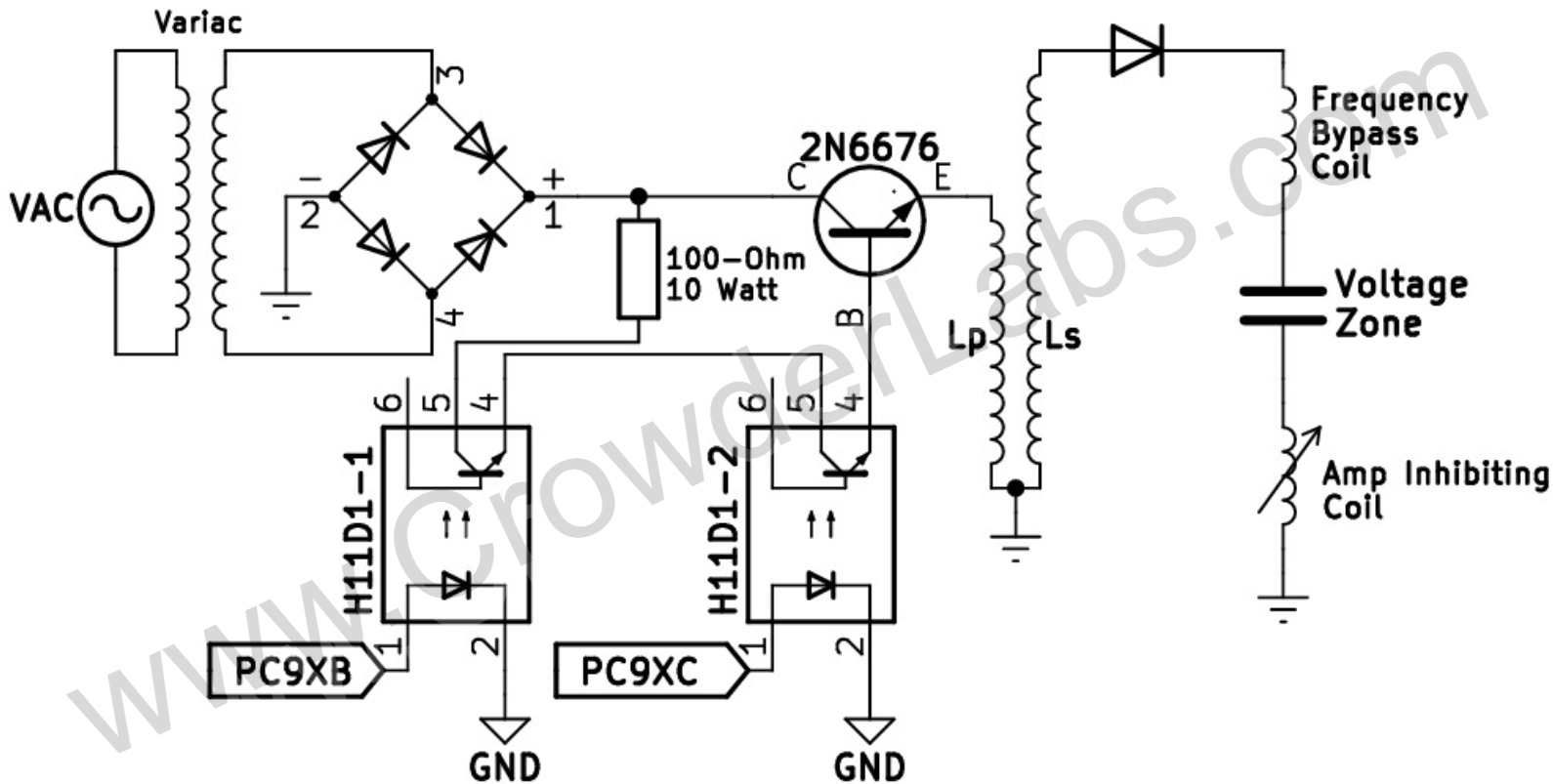

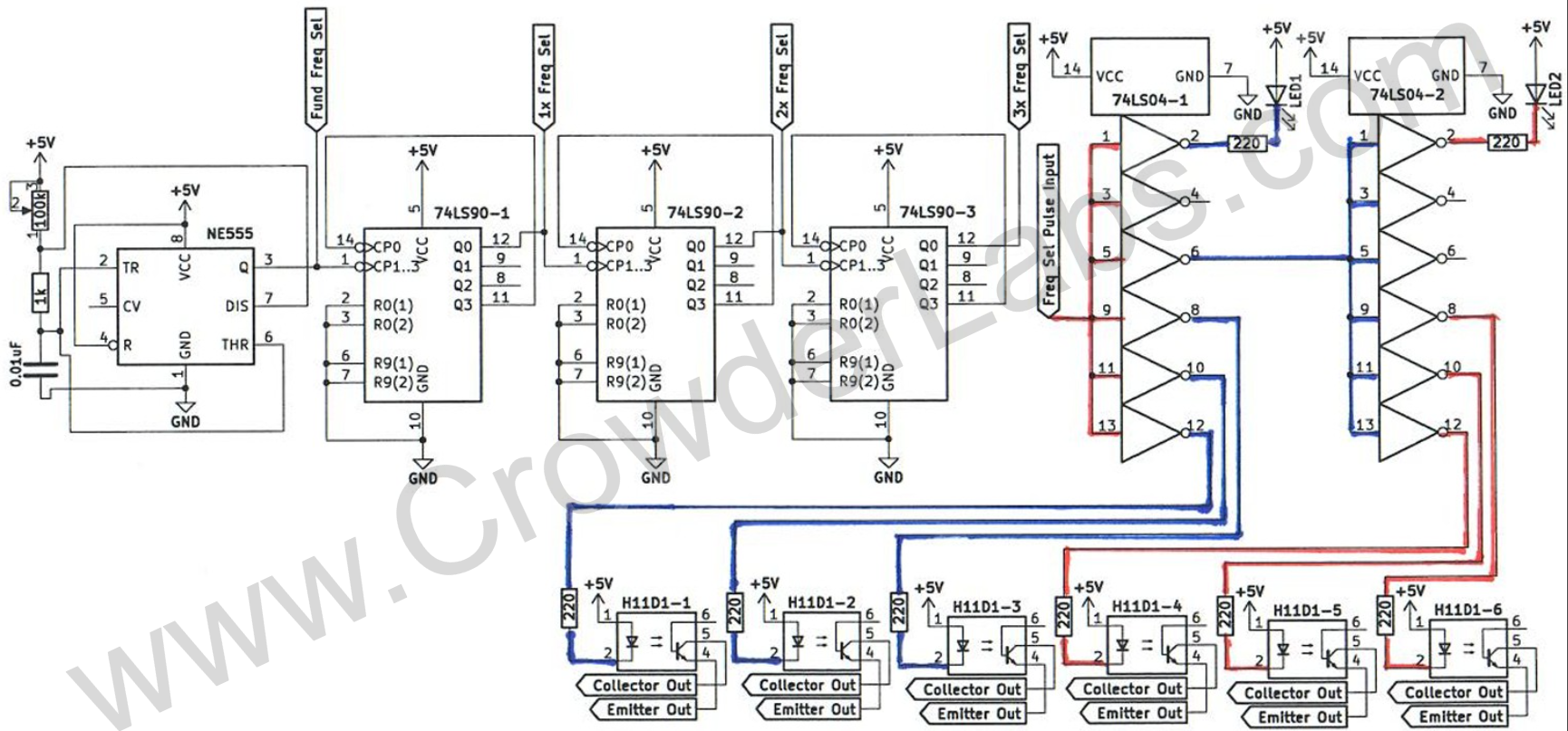

Schematic:

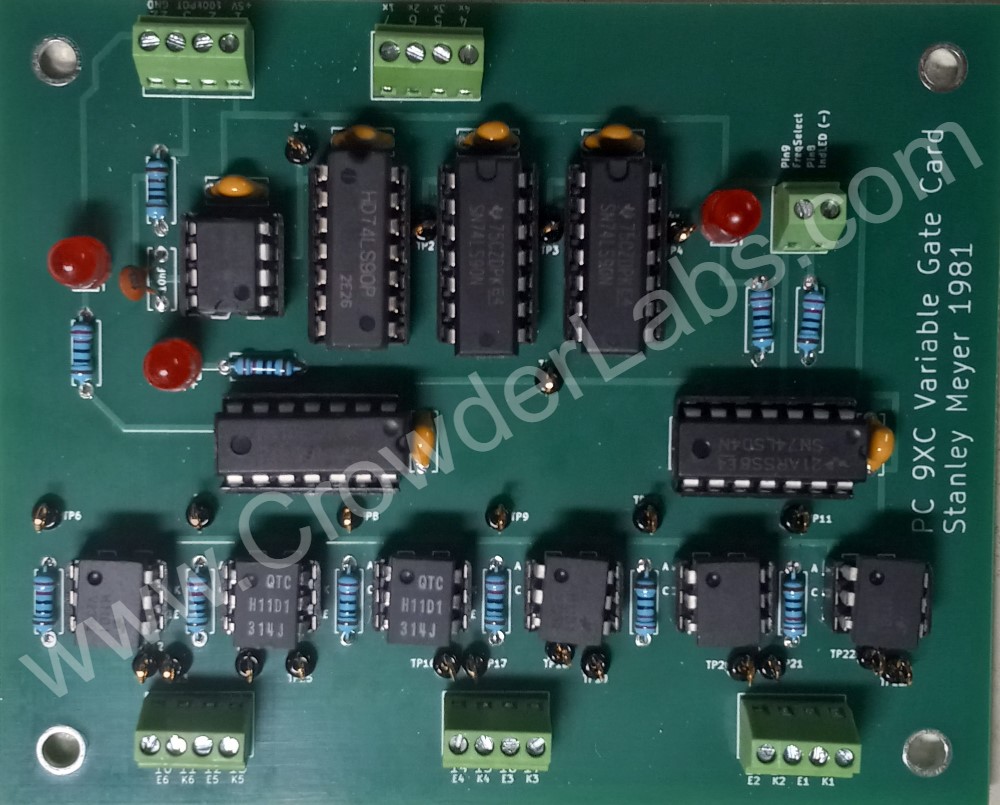

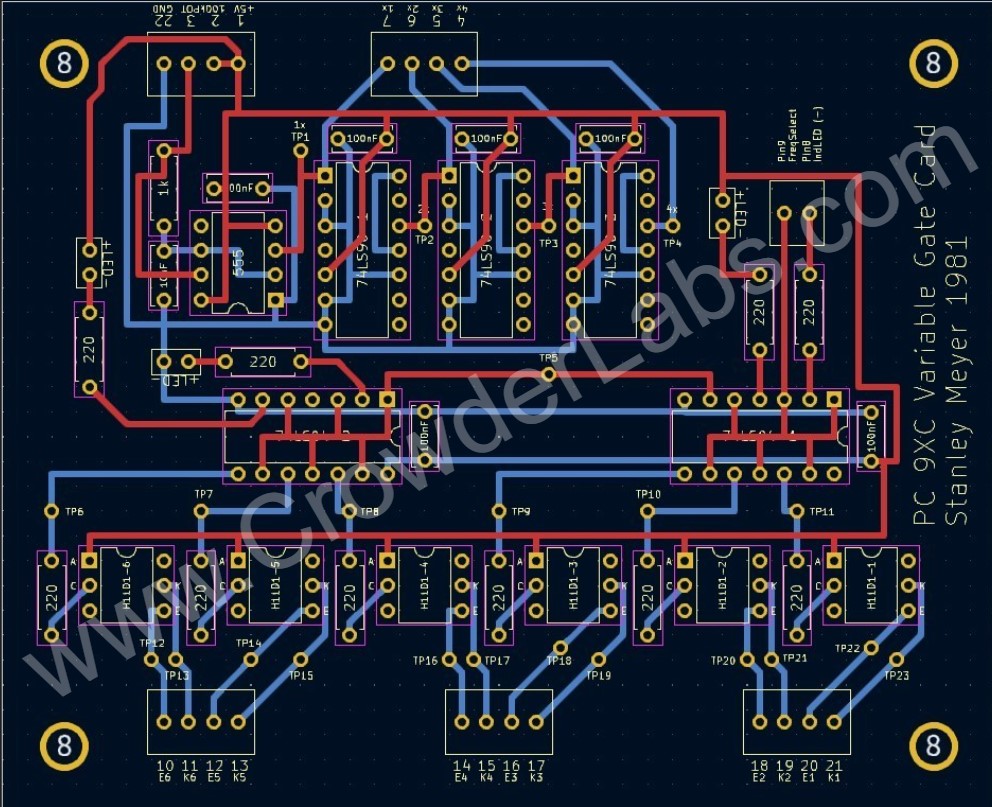

Replica PCB Top:

Please note that decoupling capacitors were added across each IC for stability and noise reduction. LEDs visually indicate when the hex inverters (74LS04-1/74LS04-2) are in opposing polarity. Photos demonstrating this functionality are within this section. PCB trace layers are shown in the photo below.

Replica PCB Traces:

Explanation:

The circuit includes an integrated variable frequency generator, with a 50% duty cycle provided by three divide-by-ten counters (74LS90), the same circuit as the PC9XB. The pulse train is communicated to two hex inverter (74LS04-1 & 74LS04-2) stages that produce 180-degree phase shifted output pulses. Put more simply, this circuit performs a flip-flopping function. Optocouplers provide isolation between control circuitry and the switching applications that will be covered herein. Having two optocouplers in series, controlling PC9XA driver BJT, produces a two input “AND” gate.

The aforementioned description of duty cycle adjustment is slightly misleading. As the frequency is decreased, the number of pulses, delivered by the PC9XB, to the excitor array is increased. Conversely, as the frequency is increased, the number of pulses is decreased. In both cases, the off time is equal to the on time due to the fixed 50% duty cycle. A better understanding can be ascertained by viewing Stan’s reference to “duty-cycle” variability within the scope of controlling the quantity of frequency pulses applied to the electrode pair.

Stan's Applications:

1.) Voltage Intensifier Circuit 9XA: Adjusting the number of pulses applied to the power transistor driving the VIC coil. Can facilitate several different pulse applications including continuous, gated and sequenced.

2.) Dual Voltage Pulsing Circuit: Adjusting the number of pulses applied to their associated power transistors driving the VIC coil. Providing two independently varied voltage pulse waveforms.

4.) Steam Resonator Circuit: Provide switching to associated power transistor to produce alternating application of positive polarity to electrodes.

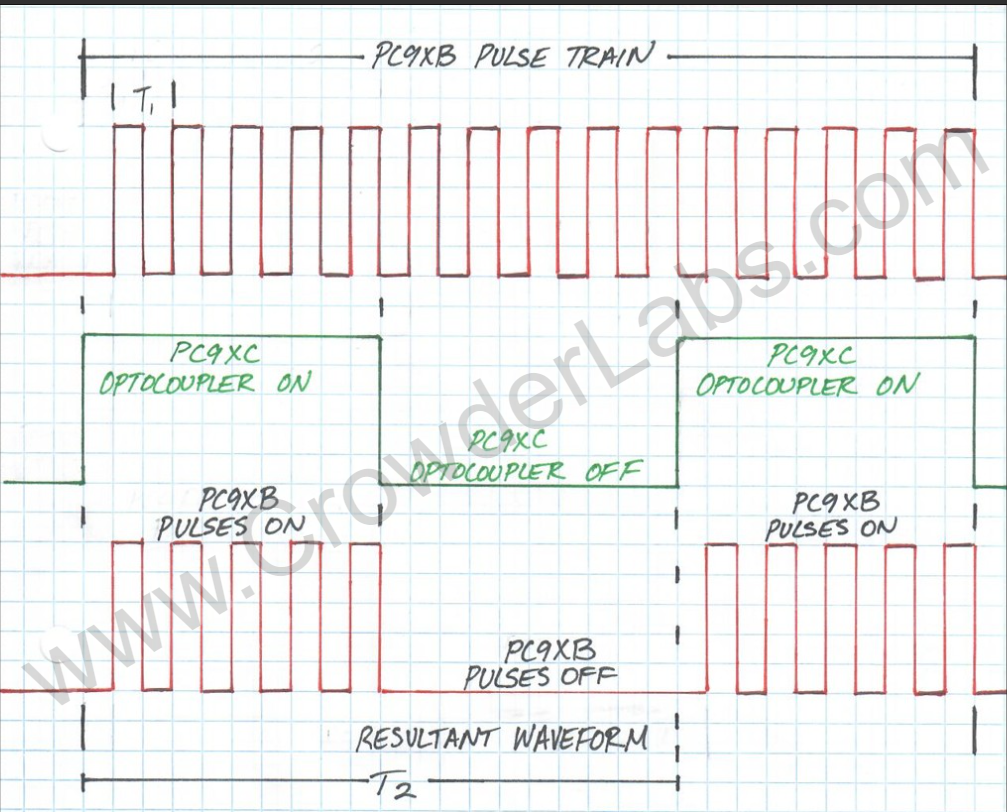

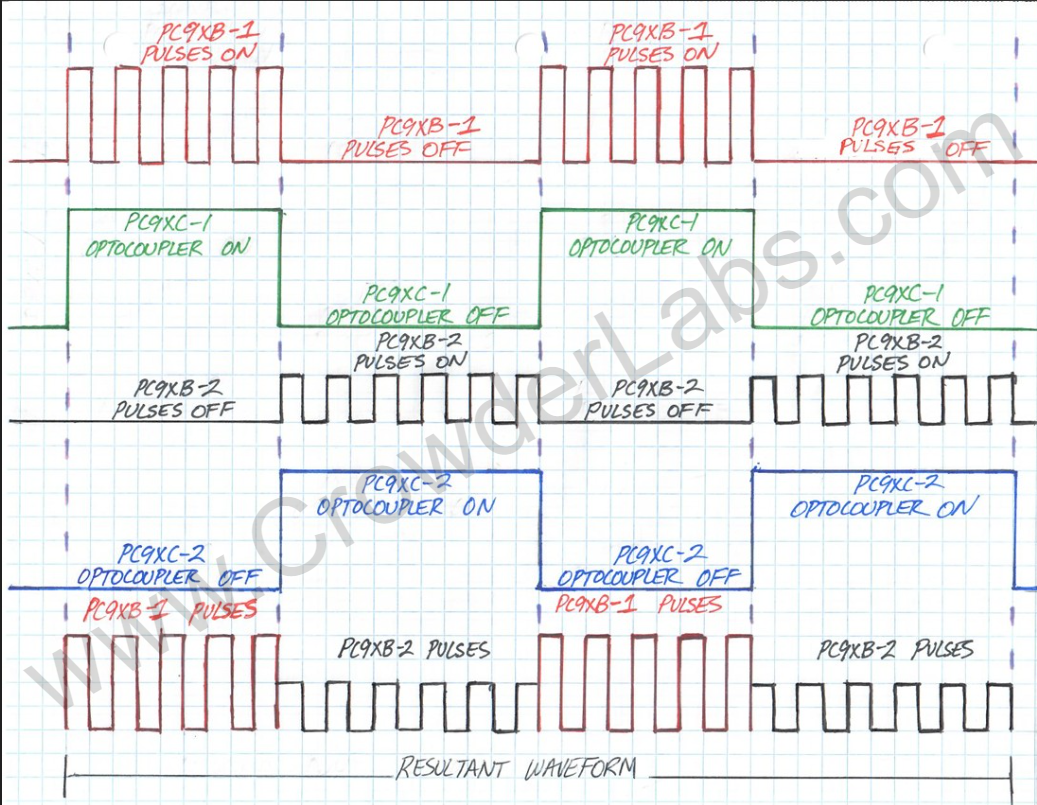

Referencing the schematic below, optocoupler “H11D1-2” controls the number of pulses per unit of time from the frequency generator, PC9XB, to be applied to power transistor’s base. Diagram 1 illustrates the waveform produced. While five pulses per half cycle are shown, both circuit’s frequencies are independently adjusted, resulting in a lack of synchronization without precise adjustments. The period of the PC9XB optocoupler pulse train is represented by T1, while T2 represents the period of the PC9XC optocoupler pulse train. It can be seen that both are fifty percent. Voltage of the resultant waveform is independently adjustable via variable transformer.

Diagram 1:

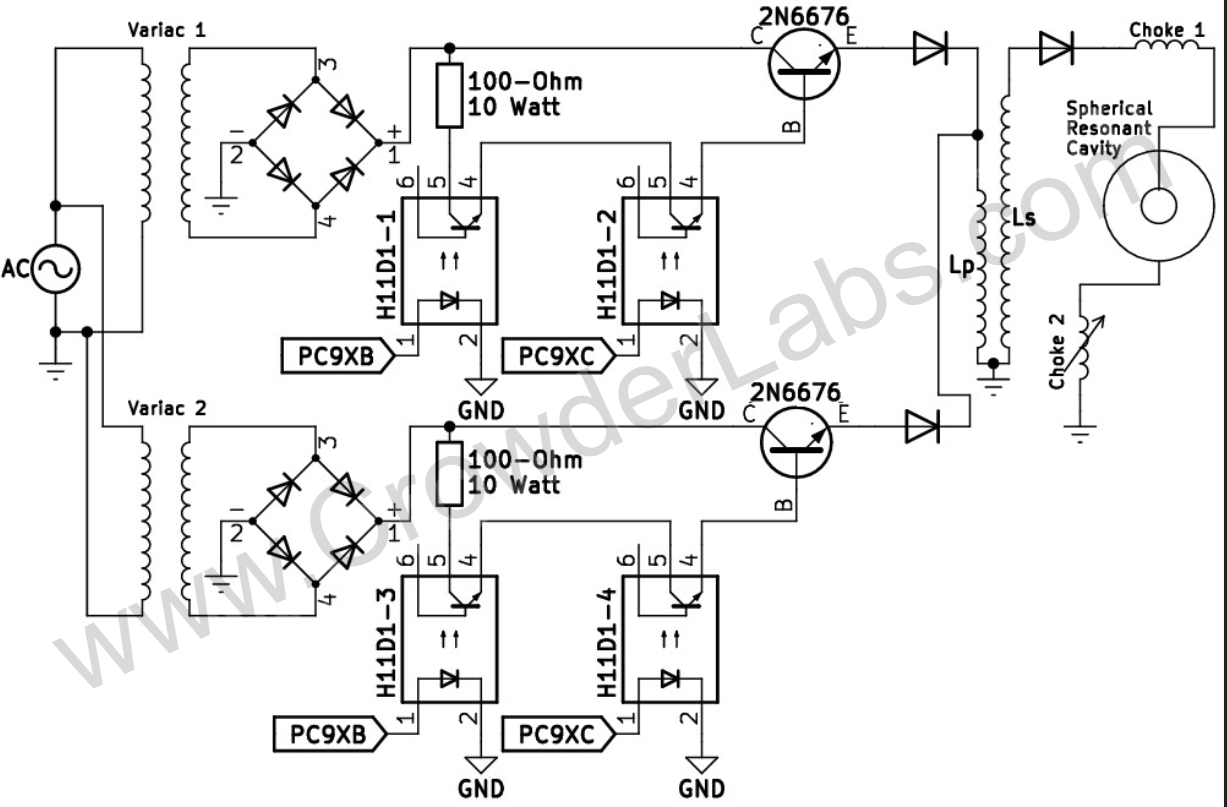

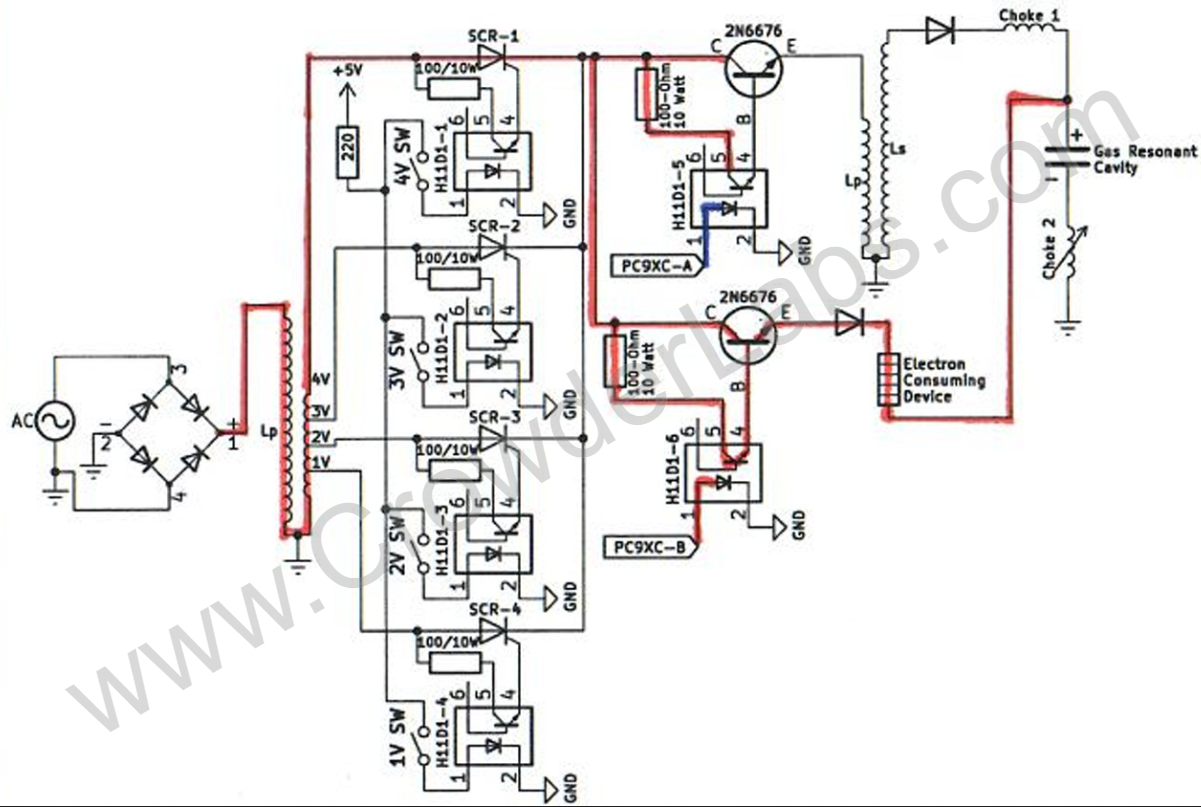

The picture below, shows another embodiment. Four separate circuits, two PC9XB’s and two PC9XC’s are utilized to produce two independently adjustable voltage gated pulse trains that are applied to a resonant cavity of a spherical geometry. Diagram 3 illustrates the waveforms during circuit operation.

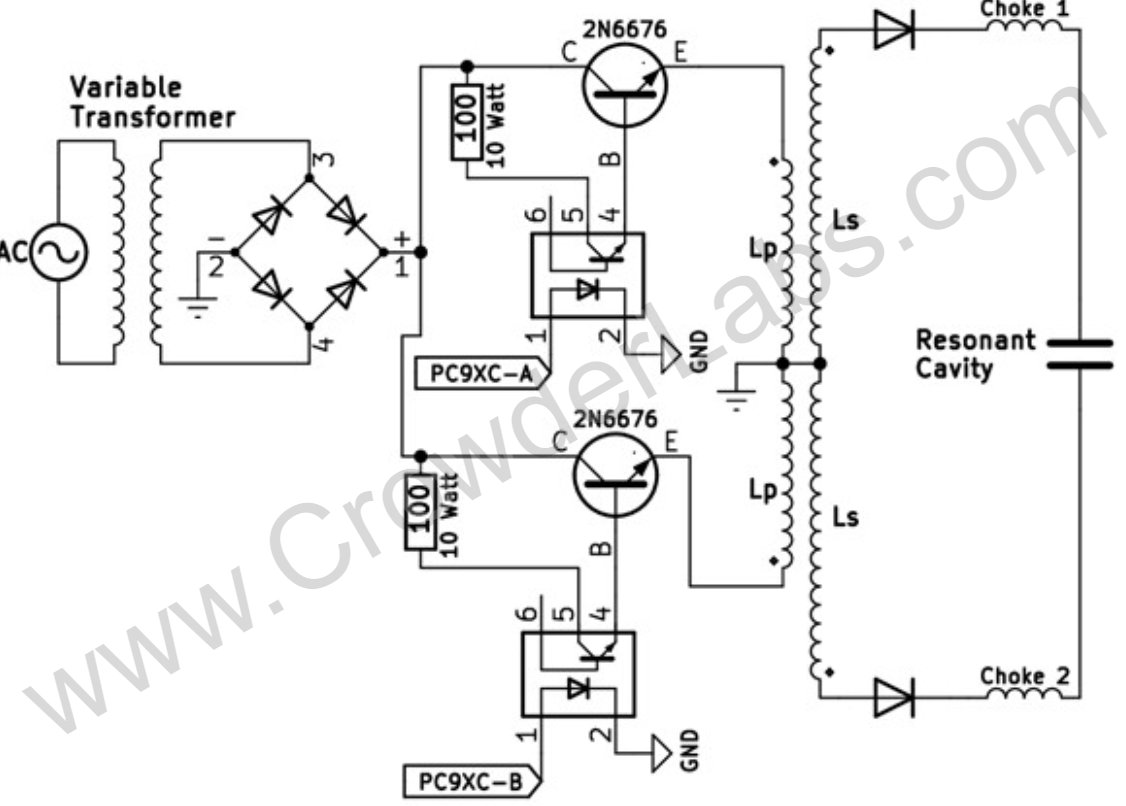

Diagram 2:

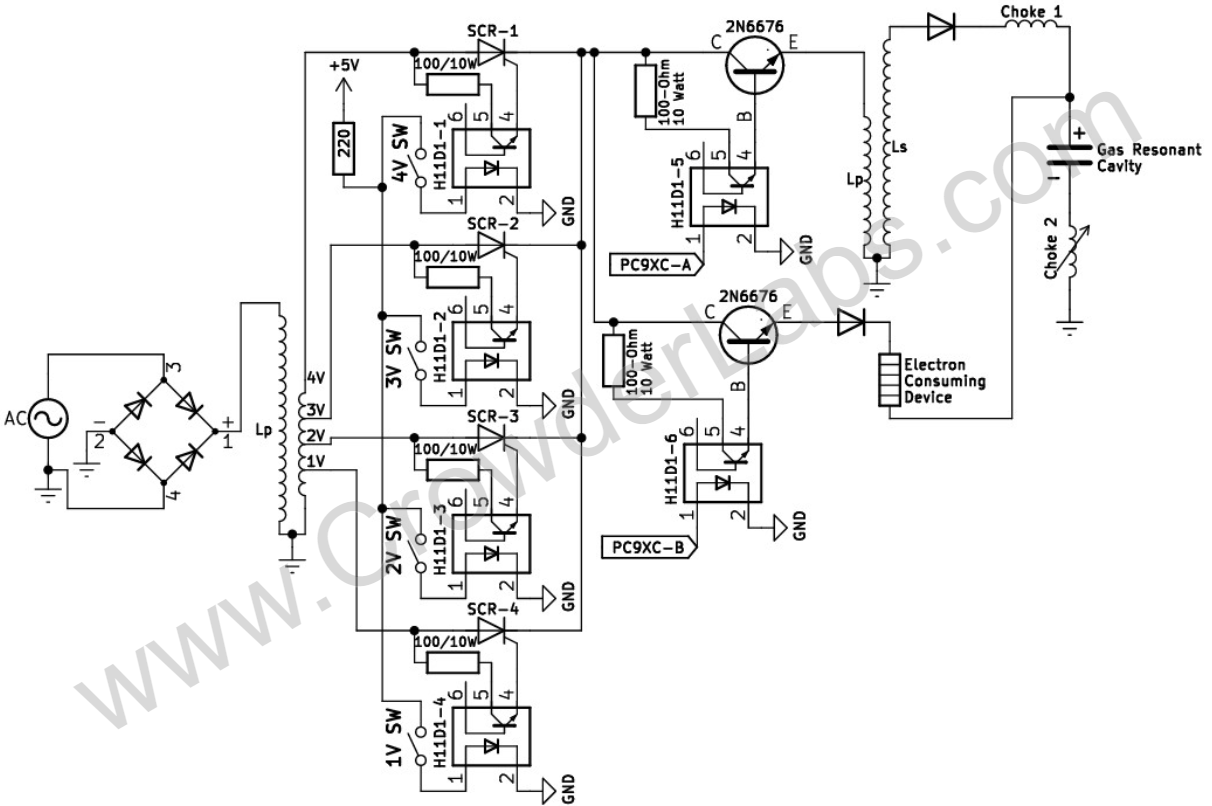

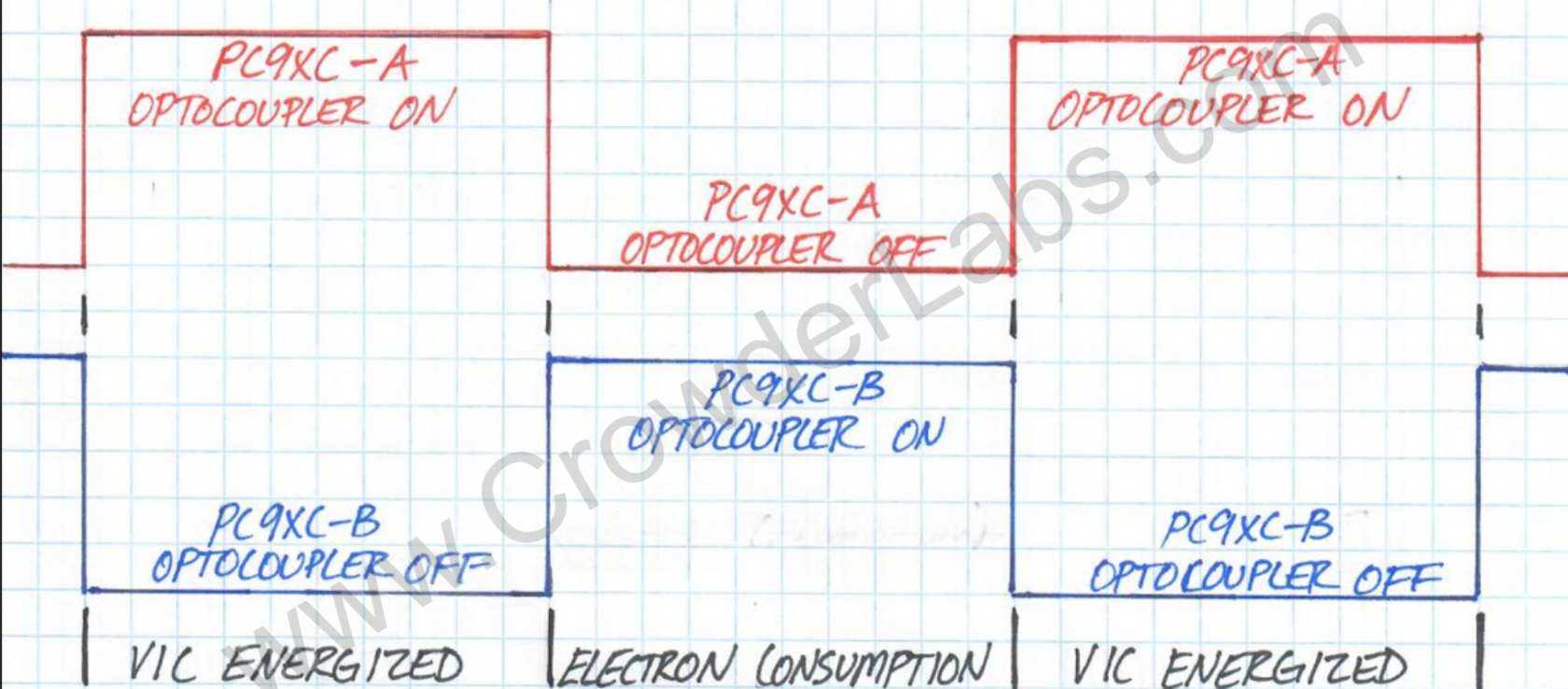

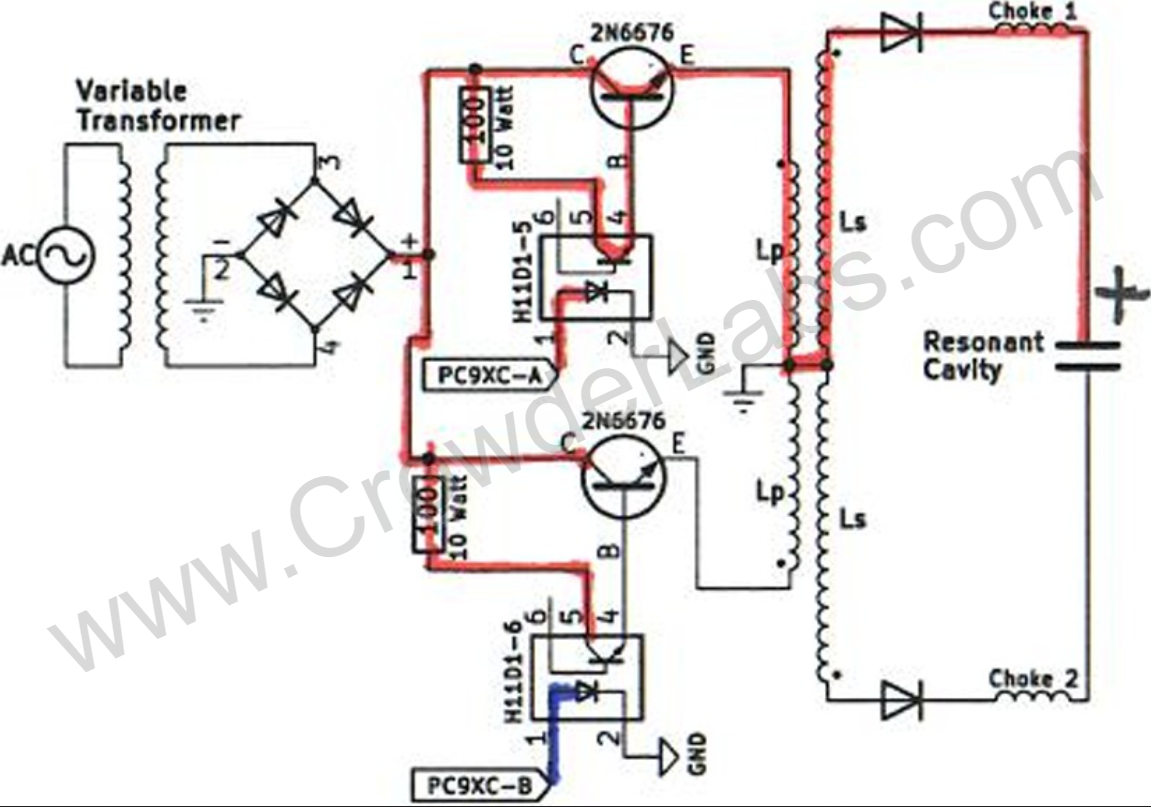

The schematic below illustrates the flip-flop switching application that facilitates electron extraction. Rectified mains supply provides a unipolar DC waveform that energizes the step-down transformer to produce a low voltage at a fixed frequency of 120Hz. Conversely, a filtering capacitance can allow a wider range of frequencies. Secondary coil taps in conjunction with switch-selected optocoupler triggered SCRs controls the voltage applied to the primary coil of the VIC step up stage (see page 79 for circuit board). The 120Hz has a superimposed gate signal via optocoupler “H11D1-5”, which is triggered via a PC9XC circuit. This optocoupler controls the number of pulses applied to the base of the power NPN. Diagram 3 details the waveform of this flip-flopping behavior.

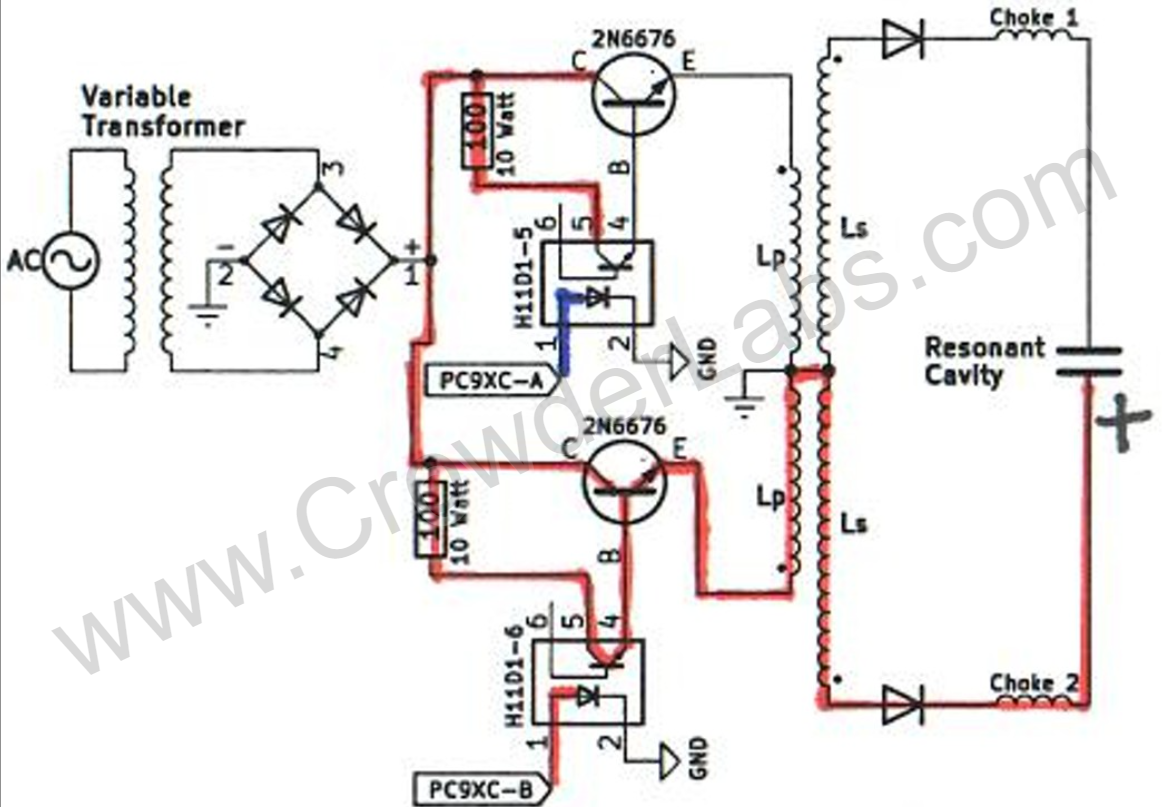

The optocoupler “H11D1-6” is triggered 180o out of phase with respect to H11D1-5. During this time, positive potential is applied to one side of the electron consuming device. This causes liberated electrons within gas resonant cavity (see Gas Resonant Cavity / Hydrogen Gas Gun section for further details) to be attracted to this positive potential which leads to flow into electron consuming device.

Diagram 3:

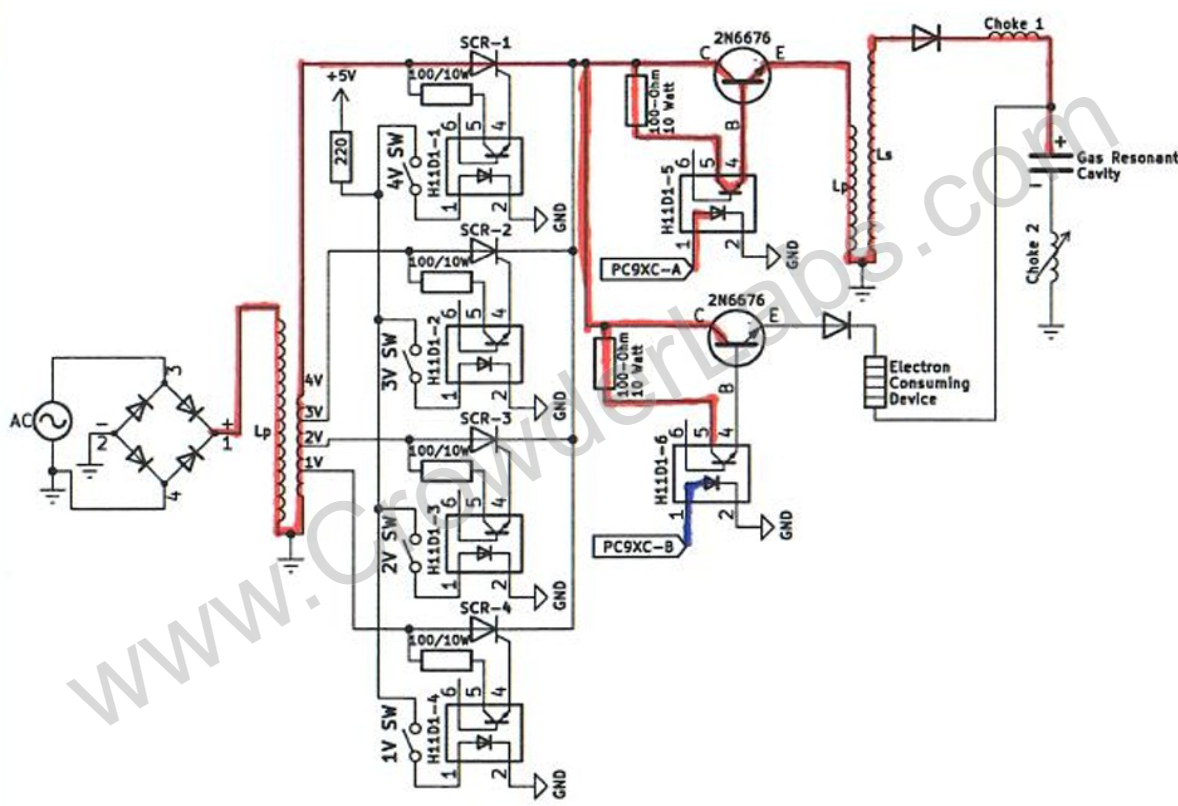

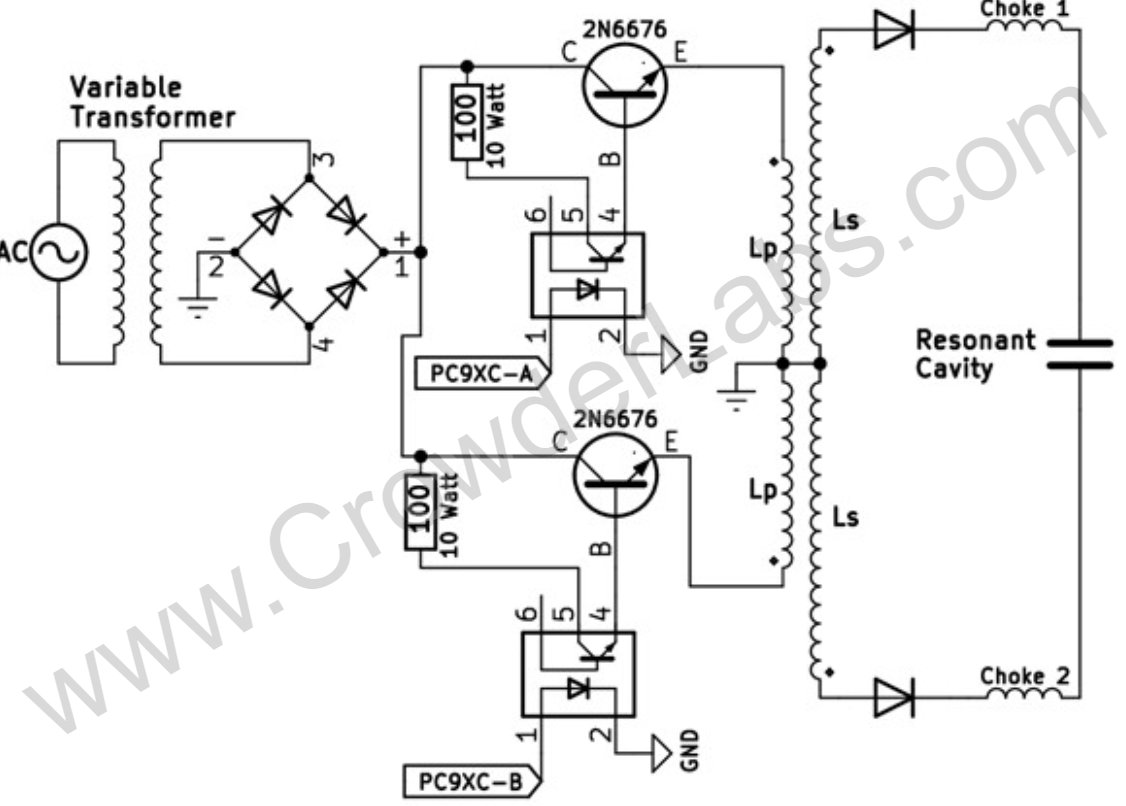

With reference to the schematic1 below, another application utilizing the flip-flopping action is illustrated for operation of the steam resonator. As shown in the aforementioned Diagram 3, the optocoupler signals, PC9XC-A and PC9XC-B are 180o out of phase with respect to one another. An adjustable rectified DC voltage is supplied, via the variable transformer, having a fixed frequency of 120Hz. During PC9XC-A triggering of the first power transistor, a unipolar rippling DC waveform is applied to the first primary coil, causing a high positive potential – via step-up transformer – to be applied to the first resonant charging choke coil, by forward biasing the series diode, onto the top plate of the resonant cavity structure. The bottom primary/secondary pair is opposite in polarity, reverse biasing the series diode, not permitting any potential to be applied to the second plate.

During PC9XC-B triggering of the second transistor, a unipolar rippling DC waveform is applied to the second primary coil, causing a higher positive potential – via step-up transformer - to be applied to the second resonant charging choke coil, by forward biasing the series diode, onto the bottom plate of the resonant cavity structure. At this time, the top primary/secondary pair is opposite in polarity, reverse biasing the series diode, not permitting any potential to be applied to the top plate.

It should be apparent, that applying a differential polarity is avoided. Only positive polarity is utilized in this arrangement, as only one pair of electrodes are present. This flip-flopping positive polarity influences the oxygen and hydrogen atoms, causing atomic/molecular flexing which produces heat energy.

Steam Resonator Logical Flow - Phase 1:

Steam Resonator Logical Flow - Phase 2:

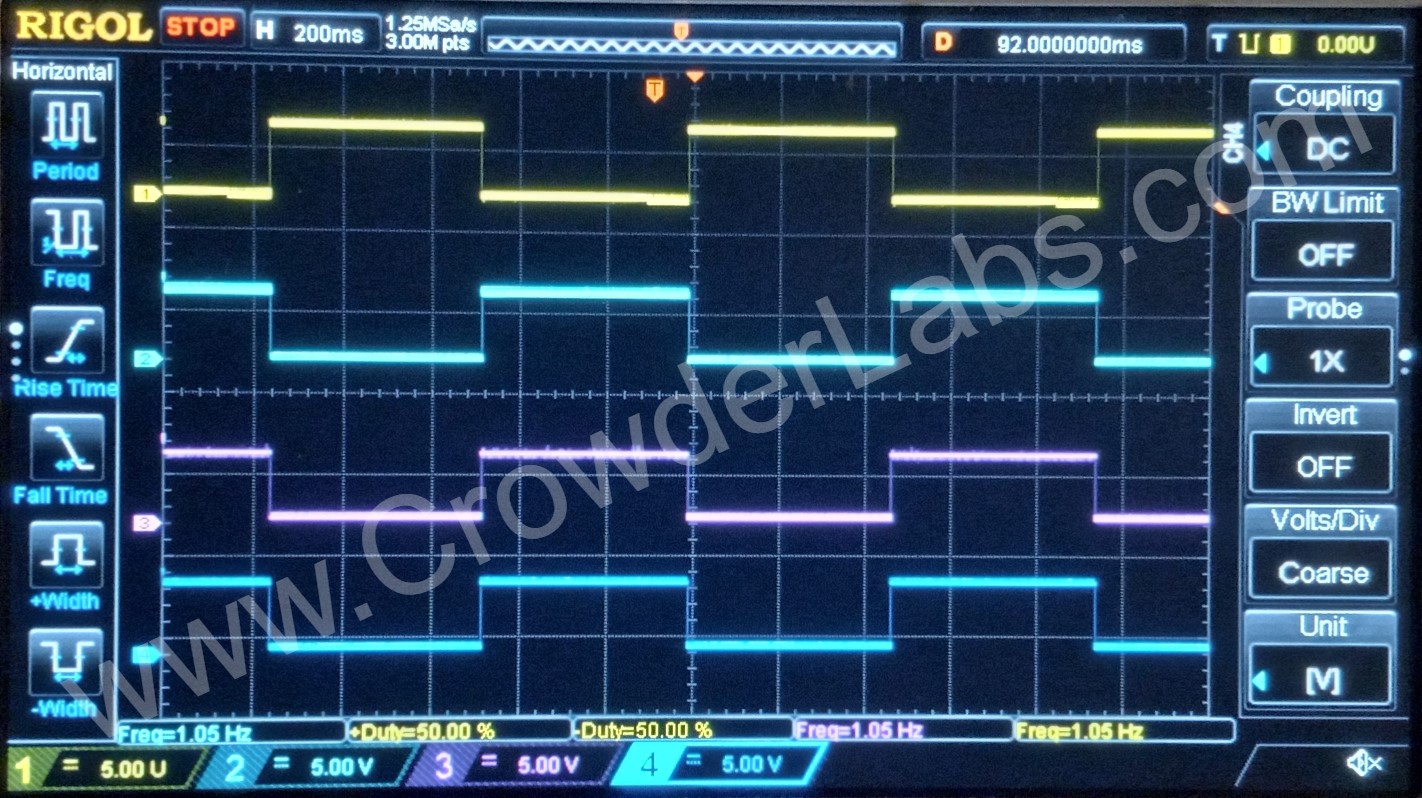

Frequency is supplied by a PC9XB arrangement (see PC9XB analysis section for refresher) where an initial frequency is divided by multiples of ten and conditioned to have a 50% duty cycle. This circuit incorporates a frequency selection capability that is provided by a rotary switch, having the pole terminal interconnected to inputs 1,3,5,9,11,13 of the first hex inverter IC (74LS04-1). The input waveform polarity is inverted as shown in the scope shot below. Channel one (yellow) is representative of the pulse frequency into input pins. Channels 2, 3 and 4 (teal, magenta, dark blue) are representative of the three channels going out to optocoupler sets associated with this first hex inverter.

74LS04-1 output pin #2 has a 220Ω, ¼ watt resistor wired in series which triggers an externally mounted LED, indicating the inverter’s LOW logic level. 74LS04-2 output pin #2 has a 220Ω, ¼ watt resistor wired in series to provide a visual indication during the opposing logic state of the 74LS04-1. Output pins #8, #10, #12 of each inverter are connected to their respective optocouplers, each having a series 220Ω, ¼ watt cathode resistor to limit the current to 20mA. Optocouplers (H11D1-1, H11D1-2, H11D1-3) are all turned ON at the same time when 74LS04-1 is in a LOW logic state. During a HIGH logic state, these optocouplers are all turned OFF.

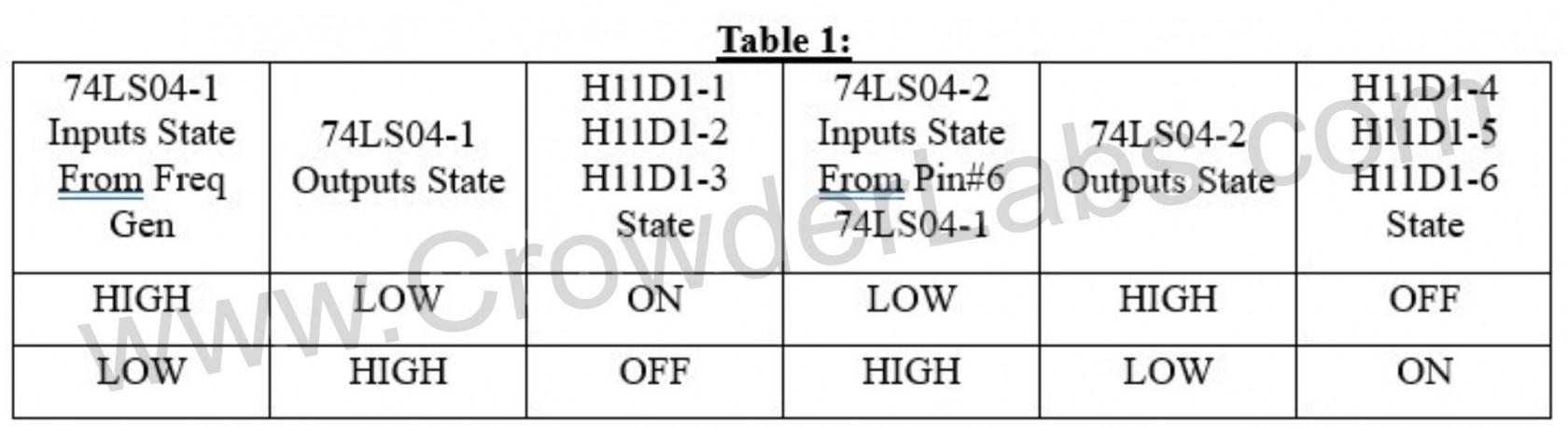

74LS04-1 output pin #6 is connected to the input pins #1, #3, #5, #9, #11, and #13 of the second hex inverter IC (74LS04-2). This produces a logical state that is inverse relative to 74LS04-1 but non-inverted relative to pulse frequency polarity (see logic chart below). Optocouplers (H11D1-4, H11D1-5, H11D1-6) are all triggered at the same time when 74LS04-2 is in a LOW logic state. During a HIGH logic state, these optocouplers are all turned OFF. Logic is summarized below in Table 1.

PC9XC Logical Flow - Phase 1:

PC9XC Logical Flow - Phase 2: